|

|

| • Integrated, ultra low power SRAM, power-fail

control circuit, and battery |

| • READ cycle time equals WRITE cycle time |

| • Automatic power-fail chip deselect and WRITE

protection |

| • WRITE protect voltages:

(VPFD = power-fail deselect voltage) |

| • M48Z35: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

|

| • M48Z35Y: 4.5 to 5.5 V;

4.2 V ≤ VPFD ≤ 4.5 V

|

| • Self-contained battery in the CAPHAT™ DIP

package

|

| • Packaging includes a 28-lead SOIC and

SNAPHAT® top (to be ordered separately) |

| • SOIC package provides direct connection for a

SNAPHAT® top which contains the battery |

| • Pin and function compatible with JEDEC

standard 32 Kbit x 8 SRAMs

|

| • RoHS compliant |

| • Lead-free second level interconnect

|

|

| CATALOG |

| M48Z58Y-70PC1 COUNTRY OF ORIGIN |

| M48Z58Y-70PC1 PARAMETRIC INFO |

| M48Z58Y-70PC1 PACKAGE INFO |

| M48Z58Y-70PC1 PACKAGING INFO |

| M48Z58Y-70PC1 ECAD MODELS |

|

| COUNTRY OF ORIGIN |

| Malaysia |

|

| PARAMETRIC INFO |

| Density (bit) |

64K |

| Type |

NVSRAM |

| Interface Type |

Parallel |

| Maximum Access Time (ns) |

70 |

| Typical Operating Supply Voltage (V) |

5 |

| Minimum Operating Temperature (°C) |

0 |

| Maximum Operating Temperature (°C) |

70 |

| Supplier Temperature Grade |

Commercial |

| Density in Bits (bit) |

65536 |

| Maximum Operating Current (mA) |

50 |

| Organization |

8Kx8 |

| Data Bus Width (bit) |

8 |

| Minimum Operating Supply Voltage (V) |

4.5 |

| Maximum Operating Supply Voltage (V) |

5.5 |

| Minimum Storage Temperature (°C) |

-40 |

| Maximum Storage Temperature (°C) |

85 |

| Operating Supply Voltage (V) |

5 |

|

| |

| PACKAGE INFO |

| Supplier Package |

PCDIP |

| Pin Count |

28 |

| PCB |

28 |

| Tab |

N/R |

| Pin Pitch (mm) |

2.79(Max) |

| Package Length (mm) |

39.88(Max) |

| Package Width (mm) |

18.34(Max) |

| Package Height (mm) |

8.89(Max) |

| Package Diameter (mm) |

N/R |

| Seated Plane Height (mm) |

8.89(Max) |

| Mounting |

Through Hole |

| Package Material |

Plastic |

| Package Family Name |

DIP |

| Jedec |

N/A |

|

| |

| PACKAGING INFO |

| Packaging |

Tube |

| Packaging Document |

Link to Datasheet |

|

| |

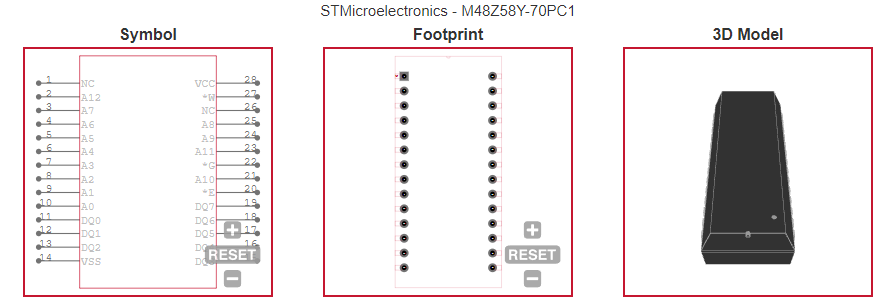

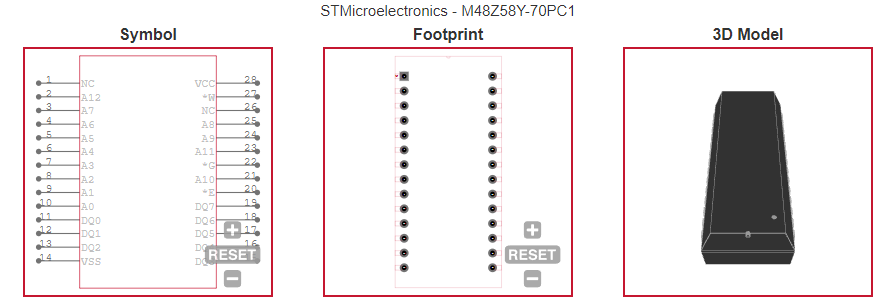

| ECAD MODELS |

|

|